这种全加器的任意一位的加法运算,都必须等到低位加法完成送来进位时才能进行.这种进位方式称为串行进位,它的缺点是运算速度慢,但其电路比较简单,因此在对运算速度要求不高的设备中,仍不失为一种可取的全加器.T692集成加法器就是这种串行加法器.

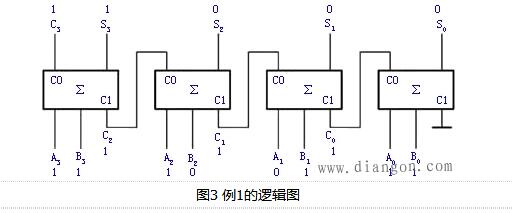

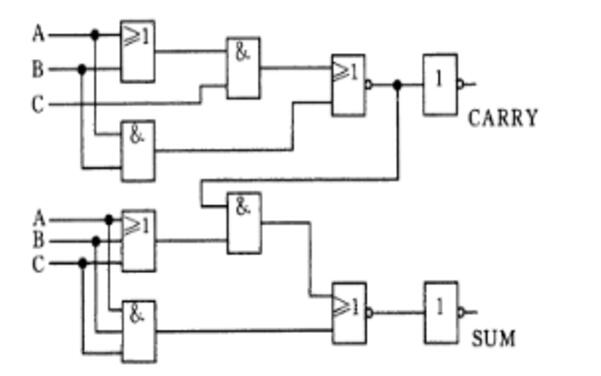

图3 例1的逻辑图 看完本文有收获?请分享给更多人 关注「电子工程专辑」,做优秀工程师! 这种全加器的任意一位的加法运算,都必须等到低位加法完成送来进位时才能进行.这种进位方式称为串行进位,它的缺点是运算速度慢,但其电路比较简单,因此在对运算速

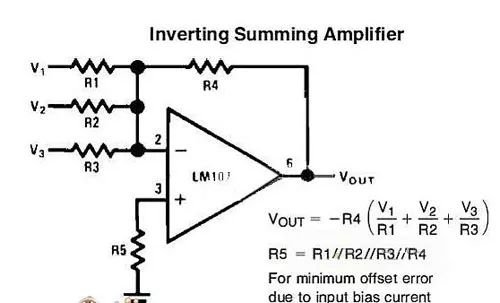

0次 内阻非常小,才不会影响计算精度.因而应用较少.反相求和电路因其\"虚地\"特性,输入阻抗极低,使各路信号输入电流以\"汇流模式\"进入输入端,不会造成各输入信号之间的电流流动,故能保障运算精度,应用较多. 四、反相加法器电路与原理(图)

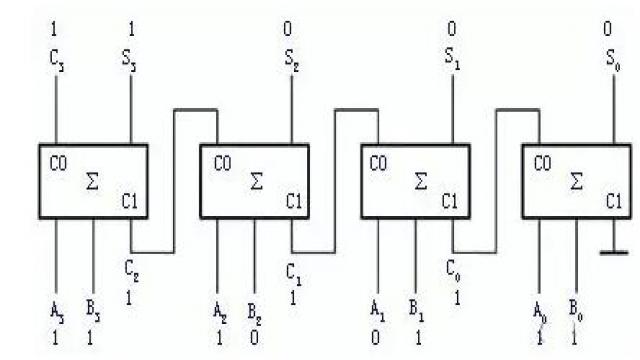

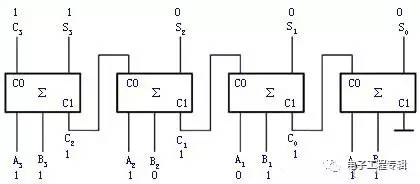

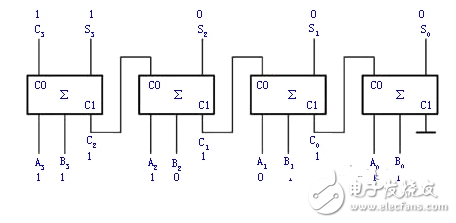

例1、用4个全加器组成一个逻辑电路以实现两个4位的二进制数A—1101(十进制为13)和B—1011(十进制为11)的加法运算. 解: 逻辑电路如图3所示,和数是S—11000(十进制数为24).根据全加器的逻辑状态表自行分析. 全加器可用两个

三、加法器内部电路图 四、加法器内部原理图 这种全加器的任意一位的加法运算,都必须等到低位加法完成送来进位时才能进行.这种进位方式称为串行进位,它的缺点是运算速度慢,但其电路比较简单,因此在对运算速度要求不高的设备中,仍不失为一种可取的全加器.T6

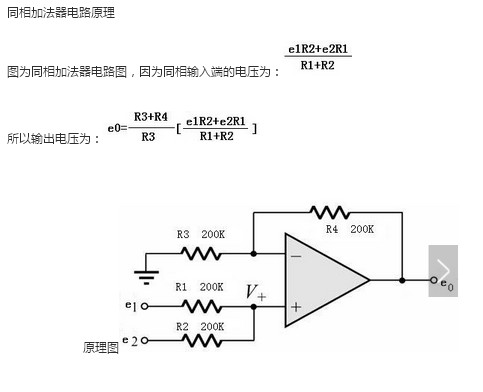

同相加法器计算 因为是同相加法器,输入阻抗高,这样信号不太容易流入加法器,反而更容易流入B端,而影响到B端的正常使用;同样,如B输入信号时,容易流入A端,而影响到A端的正常使用. 当选用反相加法器时,因为加法器输入阻抗低,不管是A端,还是B端信号,

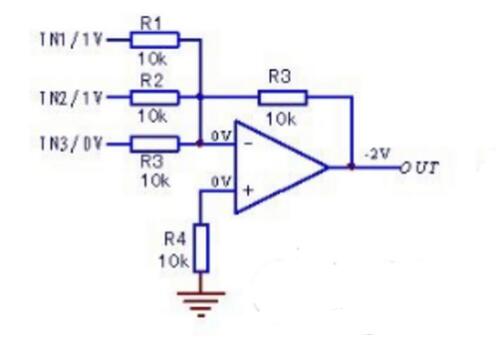

反相加法器的基本电路结构为反相放大器,由其\"虚地\"特性可知,两输入端俱为0V地电位.这就决定了电路的控制目的,是使反相输入端电位为0V(同相输入端目标值为0V).以上图a电路电路参数和输入信号值为例进行分析,则可得出如上图b所示的等效图.反相加法器的偏置电

4,此位二数相加的和S(32位),5,此位二数相加产生的进位COUT(1位). 要实现32位的二进制加法,一种自然的想法就是将1位的二进制加法重复32次(即逐位进位加法器).这样做无疑是可行且易行的,但由于每一位的CIN都是由前一位的COUT提供的,所

二进制加法器原理 被加数和加数的各位能同时并行到达各位的输入端,而各位全加器的进位输入则是按照由低位向高位逐级串行传递的,各进位形成一个进位链.由于每一位相加的和都与本位进位输入有关,所以,最高位必须等到各低位全部相加完成并送来进位信号之后才能产生运算

的运算关系中既有加法又有减法. 使用双集成运放的电路如图8.13 解(1)用反相求和电路形式(如图12)

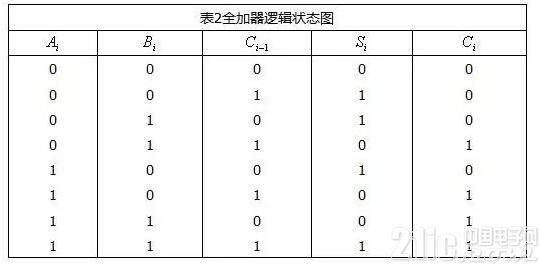

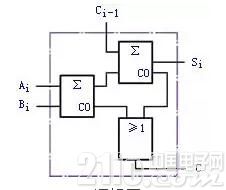

全加器可用两个半加器和一个或门组成,如图2(a)所示.在第一个半加器中相加,得出的结果再和在第二个半加器中相加,即得出全加和.两个半加器的进位数通过或门输出作为本位的进位数.图2(b)是全加器的逻辑符号. 2、全加器 当多位数相加时,半加器可用于最

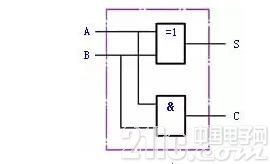

以单位元的加法器来说,有两种基本的类型:半加器和全加器. 半加器有两个输入和两个输出,输入可以标识为 A、B 或 X、Y,输出通常标识为合 S 和进制 C.A 和 B 经 XOR 运算后即为 S,经 AND 运算后即为 C. 才能开始计算,等等.而

(a)逻辑图 (b)逻辑符号 图1半加器逻辑图及其逻辑符号 2、全加器 当多位数相加时,半加器可用于最低位求和,并给出进位数.第二位的相加有两个待加数,还有一个来自低位送来的进位数.这三个数相加,得出本位和数(全加和数)和进位数,这就是\"全

(a)逻辑图 (b)逻辑符号 图2 全加器逻辑图及其逻辑符号 例1、用4个全加器组成一个逻辑电路以实现两个4位的二进制数A-1101(十进制为13)和B-1011(十进制为11)的加法运算. 解: 逻辑电路如图3所示,和数是S-1100

除非各种IN信号源内阻非常小,才不会影响计算精度.因而应用较少.反相求和电路因其\"虚地\"特性,输入阻抗极低,使各路信号输入电流以\"汇流模式\"进入输入端,不会造成各输入信号之间的电流流动,故能保障运算精度,应用较多. 四、反相加法器电路与原理(图)

这种全加器的任意一位的加法运算,都必须等到低位加法完成送来进位时才能进行.这种进位方式称为串行进位,它的缺点是运算速度慢,但其电路比较简单,因此在对运算速度要求不高的设备中,仍不失为一种可取的全加器.T692集成加法器就是这种串行加法器. 三、加法器内

网友:马拯岩:抚恤翻倍!家眷,城堡会继续养着。

网友:胡垒丞:一些中看不中用的都有一堆。

网友:钟愧:四位才会现身一次。

网友:陈皈变:你、你怎可如此狠辣,那可是火德星君之子啊,要是被火德星君知道你杀了他的独子,他又岂会放过你?”吕洞宾一拍大腿,一懊恼不已。

网友:刘针澄:甚好,今日天气晴朗,秋风习习,学生以为正是踏秋的好时机,不知先生以为如何?”表少爷恭敬的问先生道。

- 上一篇:地藏经注音版 女子念地藏经注意事项_地藏菩萨本愿经完整版

- 下一篇:返回列表